## ATLAS

## A Framework for NoC Generation and Evaluation

Aline Mello\*, Alexandre Amory<sup>†</sup>, Ney Calazans<sup>†</sup> and Fernando Moraes<sup>†</sup>

\*UPMC - LIP6 4, Place Jussieu - Paris - France Email: Aline.Vieira-de-Mello@lip6.fr <sup>†</sup>PUCRS - FACIN Av. Ipiranga, 6681 - Porto Alegre - Brazil Email: {name.surname}@pucrs.br

MultiProcessor Systems-on-Chip (MPSoCs) are becoming a much more prevalent design style, to achieve tight time-to-market design goals, to maximize design reuse, to simplify the verification process and to provide flexibility and programmability for post-fabrication reuse of complex platforms[8]. Networks-on-chip (NoCs) are the preferable the communication infrastructure to handle MPSoC communication requirements due to its scalability, power efficiency, and support to globally asynchronous locally synchronous (GALS) paradigm [13], [11], [5].

On the other hand, the NoC design - which is composed of cores connected to routers, and routers interconnected by communication channels [4] - is a more complex communication infrastructure than buses. The use of NoCs brings new challenges to the MPSoC design flow such as choosing a suitable routing algorithm, NoC topology, buffering strategy, flow control scheme, or reducing power dissipation. Due to these vast design space alternatives, the automated generation and evaluation of NoCs become a mandatory step in the MPSoCs design flow [11], [3] to establish a good trade-off between the NoC architecture characteristics and the requirements of a given application.

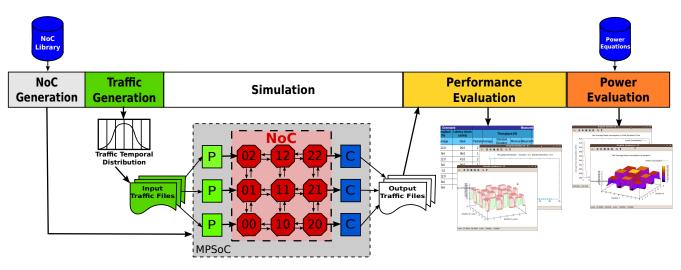

The ATLAS framework automates various processes related to the design flow of some NoCs (such as Hermes [9], Mercury, among others) proposed by the GAPH Group [6] or proposed in collaboration with other groups. Figure 1 presents the design exploration flow of the ATLAS framework.

Fig. 1. ATLAS design exploration flow

The ATLAS framework contains the following tools:

- The NoC Generation tool generates the network according to the configuration of following parameters: network dimension; communication channel width; buffer depth; flow control (handshake or credit based); number of virtual channels; scheduling algorithm (round robin or priority); and routing algorithm (XY, west-first, etc). The generated NoC is described in VHDL and its testbenches are described in SystemC.

- 2) The **Traffic Generation** tool produces different traffic patterns, for different injection rates and source/target pairs (e.g. random and complement). As described in [12], one important concept in traffic modeling is the packet timestamp, which defines the ideal moment that a packet should be inserted into the NoC by a producer (P in Figure 1). The packet timestamp is calculated according different temporal traffic distribution (e.g. normal, uniform and exponential).

- 3) The Simulation tool invokes a external VHDL/SystemC simulator: ModelSim. All generated traffic files are interpreted and injected to the NoC. During the simulation, consumers (C in Figure 1) generate output files that are read by the traffic analysis module, when the simulation finishes, allowing to compute the latency and throughput for each packet.

- 4) The Traffic Evaluation tool verifies if all packets were correctly received, and generates basic statistic data (e.g. a report file and charts) concerning time to deliver packets. The report file presents some traffic analysis results, such as: (i) total number of received packets, (ii) average time to deliver the packets, (iii) total time to deliver all packets and (iv) the average, minimal, maximal and standard deviation time to deliver a packet.

- 5) The **Power Evaluation** tool uses an estimation model [7] to generate NoC power results (e.g. power reports and charts). ATLAS contains a set of predefined equations annotated using a commercial power estimation tool (Synopsys PrimePower). These equations give the energy consumption and power dissipation according to the injection rate at each router port.

The main contribution of the ATLAS framework is to enable the designer to quickly evaluate the performance and power consumption of different NoC configurations, allowing optimize a NoC for a specific application or a set of them. NoCs generated by the ATLAS framework have been successfully prototyped in Xilinx FPGAs and have been used in industrial telecommunication applications [2], [10].

ATLAS is written in Java, allowing its execution in different hardware/software platforms. It also has an intuitive GUI which helps the designer to configure the NoC. The ATLAS framework is an active development project, with contributors and users from different countries, where new features are being included continuously. The latest version of ATLAS is freely available at [1] for download.

## REFERENCES

- [1] ATLAS. Atlas main page. https://corfu.pucrs.br/redmine/projects/atlas.

- [2] E. Bastos, E. Carara, D. Pigatto, N. Calazans, and F. Moraes. Motim a scalable architecture for ethernet switches. In Proceedings of the IEEE Computer Society Annual Symposium on VLSI, pages 451–452, 2007.

- [3] L. Benini. Application specific noc design. In Proceedings of the conference on Design, automation and test in Europe: Proceedings, DATE '06, pages 491–495, 3001 Leuven, Belgium, 2006. European Design and Automation Association.

- [4] L. Benini and G. De Micheli. Networks on chips: A new soc paradigm. Computer, 35:70-78, January 2002.

- [5] T. Bjerregaard and S. Mahadevan. A survey of research and practices of network-on-chip. ACM Comput. Surv., 38, June 2006.

- [6] GAPH. Gaph main page. https://corfu.pucrs.br/tikiwiki/tiki-index.php.

- [7] G. Guindani, C. Reinbrecht, T. Raupp, N. Calazans, and F. G. Moraes. Noc power estimation at the rtl abstraction level. VLSI, IEEE Computer Society Annual Symposium on, 0:475–478, 2008.

- [8] G. Martin. Overview of the mpsoc design challenge. In DAC, pages 274-279, 2006.

- [9] F. Moraes, N. Calazans, A. Mello, L. Möller, and L. Ost. Hermes: an infrastructure for low area overhead packet-switching networks on chip. Integr. VLSI J., 38:69–93, October 2004.

- [10] F. G. Moraes, E. A. Carara, D. V. Pigatto, and N. L. Calazans. Motim: an industrial application using nocs. In Proceedings of the 21st annual symposium on Integrated circuits and system design, SBCCI '08, pages 182–187, 2008.

- [11] P. P. Pande, C. Grecu, M. Jones, A. Ivanov, and R. Saleh. Performance evaluation and design trade-offs for network-on-chip interconnect architectures. *IEEE Trans. Comput.*, 54:1025–1040, August 2005.

- [12] L. Tedesco, A. Mello, D. Garibotti, N. Calazans, and F. Moraes. Traffic generation and performance evaluation for mesh-based nocs. In *Proceedings of the 18th annual symposium on Integrated circuits and system design*, SBCCI '05, pages 184–189, New York, NY, USA, 2005. ACM.

- [13] W. Wolf. The future of multiprocessor systems-on-chips. In Proceedings of the 41st annual Design Automation Conference, DAC '04, pages 681–685, New York, NY, USA, 2004. ACM.